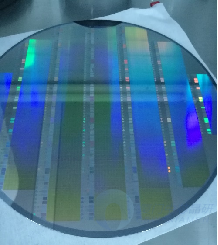

硅基砷化镓(GaAs)外延片

大数据时代的信息处理需求快速增长,推动集成电路技术不断创新。硅基光电子学通过光互联技术解决了传统电互联面临的延时与功耗瓶颈,成为提升数据传输效率的重要方向。然而,由于硅(Si)是间接带隙半导体,其发光性能较差,这为光源集成带来了挑战。通过在硅衬底上异质外延Ⅲ-Ⅴ族半导体材料(如砷化镓 GaAs),能够实现高质量激光器的单片集成,不仅有效弥补了硅的缺陷,还为大规模光子集成芯片的发展开辟了新路径。此外,硅基 GaAs 晶片在制造激光器、光电探测器和太阳能电池等器件展现出广阔的市场潜力。可供GaAs/Si外延片,大致参数如下:

1. 硅基砷化镓外延片规格参数

| 产品 | GaAs on Si (001) |

| 尺寸 | 3~8 英寸 |

| 穿透位错密度 | 1×106cm2~10×106cm2 |

| 表面平整度 | ~1nm |

| GaAs厚度 | 1.2~2um |

2. 图形化硅衬底在异质外延中的优势

近年来,图形化硅衬底因其独特优势,成为硅基Ⅲ-Ⅴ族材料外延技术的重要研究方向。图形化硅衬底通常通过在硅表面沉积一层掩膜(如 SiO₂ 或 Si₃N₄),然后采用刻蚀技术生成具有特定几何形状的图案窗口。

图形化衬底在外延生长中的优势包括:

1)位错抑制:掩膜边缘和开口侧壁可以阻挡位错的传播,显著降低外延层的位错密度;

2)应力缓解:外延材料仅在窗口区域选择性生长,减少了衬底与外延层的直接相互作用,从而有效降低应力;

3)灵活性:掩膜图案为集成电路生长提供了灵活性,简化了工艺流程,提升了重复性。

在 GaAs/Si 外延体系中,典型的图形掩膜包括条状和孔状设计。通过这些图案,可在外延过程中实现显著的晶体质量提升。

3. 具有位错滤波层的硅衬底上外延砷化镓研究

有研究团队在不同厚度的 Si 衬底上使用三种位错滤波层(DFL),通过金属有机化学气相沉积(MOCVD)成功实现了高质量 GaAs 外延层的制备。实验发现:

1)在 725 μm 厚的 Si 衬底上生长的 GaAs 薄膜表现出原子级平坦表面,均方根粗糙度为 1.288 nm,最低穿透位错密度(TDD)仅为2.4 × 107 cm−2;

2)应变缓解与缺陷阻断:压应变InGaAs/GaAs DFL 层显示出优异的位错阻挡效果,有效防止穿透位错密度 的传播;

3)晶格匹配与热应力优化:InGaP/GaAs DFL 在降低穿透位错密度方面优于AlGaAs/GaAs DFL,并在热应力缓解方面表现更佳。

研究表明,应变位错滤波层技术可以实现 Si 衬底上 GaAs 的大规模集成,并展现出低弯曲和低缺陷密度的优异特性。

更多硅基砷化镓外延片信息或疑问,请来邮咨询:vp@honestgroup.cn