3C-SiC 同质外延片

晶圆级立方SiC(3C-SiC,β-SiC)是一种有前景的MOSFET器件材料,相较于4H-SiC,其界面态密度较低,沟道迁移率较高。6H和4H-SiC MOSFET的性能不佳与位于导带边缘附近的带隙中的界面态有关,这限制了沟道中电子的传输。而3C-SiC由于带隙较小而具有较低的临界电场值,因此,与4H和6H-SiC器件相比,3C-SiC器件的比结电容将更低。这使得3C-SiC半导体材料成为是600V~1200V功率器件的理想材料。我司可供3C-SiC同质外延片,参数详情请见下表。

1. 3C-SiC同质外延片规格

| 产品 | 3C-SiC同质外延片 | |

| 衬底 | ||

| 尺寸 | 4、6英寸 | |

| 导电类型 | N型 | |

| 晶向 | (0001)偏4° | |

| 电阻率 | ≤1mΩ.cm | |

| 主定位边方向 | {1-10}±5.0° | |

| 主定位边长度 | 32.5mm±2mm、47.5mm±2mm | |

| 表面处理 | 双面抛光 | |

| 外延层 | ||

| 导电类型 | N、P型 | |

| 表面粗糙度 | ≤2nm | |

| 厚度 | 范围 | 5~100um |

| 公差 | ±10% | |

| 均匀性 | ≤4% | |

| 载流子浓度 | 范围 | 1E15~5E16cm-3 |

| 公差 | ±15% | |

| 均匀性 | ≤10% | |

应用:

3C-SiC外延在功率电子器件,比如MOSFET、二极管等,高频器件如射频器件,高温或恶劣环境下的传感器等器件方面具有应用前景。

2. 基于3C-SiC同质外延研究

2.1 3C-SiC同质外延的堆垛层错缺陷

研究人员在同质外延生长之前,在HNO3和HF溶液中通过蚀刻工艺去除硅衬底,而后采用CVD法沉积,实现的3C-SiC同质外延样品。通过HR-XRD和STEM分析实现了3C-SiC材料上堆垛层错缺陷的详细表征,显示了同质外延材料中这种缺陷类型的行为。此外,研究发现3C-SiC厚膜的同质外延生长可以降低堆垛层错密度,特别是使用缓慢的生长速率有利于堆垛层错闭合。因此,同质外延可以减少材料中的缺陷。

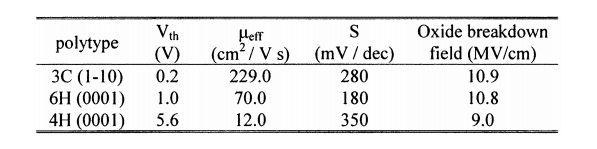

2.2 3C-SiC 同质外延MOSFET

已有研究证明,通过CVD法在3C-SiC衬底上外延生长的3C-SiC薄膜上制造的MOSFET可以产生具有高效沟道迁移率和高氧化物击穿电压的器件。这些器件表现出优异的栅控线性和饱和工作状态。随着衬底生长和工艺优化的进一步改进,预计可使用3C-SiC制备更高效的沟道迁移率器件。

图1 基于不同多晶型SiC制备的n沟道MOSFET性能对比

更多3C-SiC同质外延片信息或疑问,请邮件咨询:vp@honestgroup.cn

参考文献

[1] Nishino K , Kimoto T , Matsunami H .Photoluminescence of Homoepitaxial 3C-SiC on Sublimation-Grown 3C-SiC Substrates[J].Japanese Journal of Applied Physics, 1995, 34(Part 2, No. 9A):L1110-L1113.DOI:10.1143/JJAP.34.L1110.

[2] Lee K K , Ishida Y , Ohshima T ,et al.N-channel MOSFETs fabricated on homoepitaxy-grown 3C-SiC films[J].IEEE Electron Device Letters, 2003, 24(7):466-468.DOI:10.1109/LED.2003.815006.